先进封装技术全解析,台积电CoWoS如何突破性能瓶颈

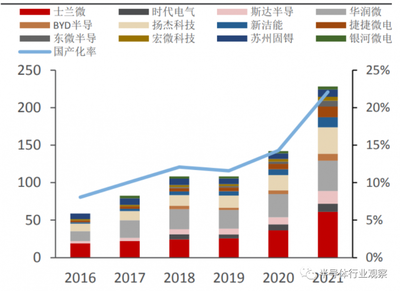

在当今高速发展的半导体行业,先进封装技术正逐渐成为提升芯片性能的关键。其中,台积电的 CoWoS(Chip on Wafer on Substrate)技术以其卓越的性能和创新的架构,在突破性能瓶颈方面取得了显著的成就。

封装技术的重要性不可忽视。随着芯片集成度的不断提高,传统的封装方式已难以满足高性能计算和移动设备等领域对芯片性能的需求。先进封装技术能够将多个芯片或不同功能的模块集成在一个封装中,实现更高的性能、更低的功耗和更小的尺寸。

台积电的 CoWoS 技术是一种基于硅中介层的三维封装技术。它通过将多个芯片堆叠在一个硅中介层上,然后再将硅中介层与基板连接,实现了芯片之间的高密度互连和高效散热。这种技术不仅能够提高芯片的性能,还能够降低生产成本和提高生产效率。

CoWoS 技术的突破性能瓶颈主要体现在以下几个方面。

高密度互连是 CoWoS 技术的核心优势之一。通过在硅中介层上制作高密度的互连结构,能够实现芯片之间的高速数据传输和低延迟通信。相比传统的封装技术,CoWoS 技术能够将互连密度提高数倍甚至数十倍,从而大大提高芯片的性能。例如,在高性能计算领域,CoWoS 技术能够将多个 GPU 芯片集成在一个封装中,实现更高的计算能力和图形处理性能。

高效散热是 CoWoS 技术的另一个重要特点。在芯片集成度不断提高的情况下,散热问题日益突出。CoWoS 技术通过将芯片堆叠在硅中介层上,并采用高效的散热设计,能够有效地将芯片产生的热量散发出去,保证芯片的稳定运行。例如,台积电采用了热传导性能优异的硅中介层材料,并在硅中介层上设置了散热通道和散热片,能够有效地提高散热效率,降低芯片的温度。

CoWoS 技术还具有灵活性和可扩展性。由于硅中介层可以根据不同的应用需求进行定制设计,因此 CoWoS 技术能够适应各种不同类型的芯片和封装需求。无论是高性能计算芯片、移动设备芯片还是物联网芯片,都可以采用 CoWoS 技术进行封装。CoWoS 技术还可以通过堆叠更多的芯片或增加硅中介层的层数来实现更高的性能和更大的集成度,具有很强的可扩展性。

CoWoS 技术的发展也面临着一些挑战。硅中介层的制作工艺复杂且成本较高,需要先进的半导造设备和工艺技术。芯片堆叠过程中的对准精度和互连可靠性也是需要解决的问题。任何微小的对准误差或互连故障都可能导致芯片性能下降甚至失效。

为了克服这些挑战,台积电不断投入研发资源,不断优化 CoWoS 技术的制作工艺和性能。例如,台积电采用了先进的光刻和刻蚀技术来提高硅中介层的制作精度和质量;采用了高精度的对准技术来确保芯片堆叠的对准精度;采用了可靠性测试和评估方法来保证互连的可靠性。

台积电的 CoWoS 技术以其高密度互连、高效散热、灵活性和可扩展性等优势,在突破性能瓶颈方面取得了显著的成就。随着半导体技术的不断发展,CoWoS 技术将在未来的芯片封装领域发挥更加重要的作用,为高性能计算、移动设备和物联网等领域的发展提供强有力的支持。